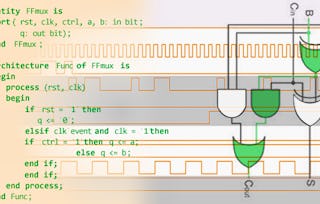

This comprehensive, hands-on course equips learners with the practical skills needed to design real hardware using SystemVerilog. Through a structured four-module progression, you will master the fundamentals of RTL development starting from basic modules and data types, moving into advanced constructs like structs, enums, and generate blocks, and culminating in the design of a fully functional digital calculator. Each module includes hands-on exercises, simulation-based assignments and guided coding practice

通过 Coursera Plus 提高技能,仅需 239 美元/年(原价 399 美元)。立即节省

您将学到什么

Design synthesizable SystemVerilog modules and integrate combinational and sequential logic to form complete digital subsystems.

Implement an Arithmetic Logic Unit (ALU) capable of performing core operations and basic arithmetic for calculator functionality.

Develop a finite state machine (FSM) to control complex system modes (calculator modes), user inputs, and operation sequencing.

Simulate, verify, and debug SystemVerilog designs to ensure functionality of the full calculator system.

您将获得的技能

- Analysis

- Software Design

- Hardware Design

- Programming Principles

- Systems Design

- Verification And Validation

- Application Specific Integrated Circuits

- Process Optimization

- Computer Engineering

- Data Synthesis

- Design

- Electronic Systems

- Data Structures

- Embedded Systems

- Simulation and Simulation Software

- Test Engineering

要了解的详细信息

可分享的证书

添加到您的领英档案

最近已更新!

February 2026

作业

1 项作业

授课语言:英语(English)

了解顶级公司的员工如何掌握热门技能

从 Design and Product 浏览更多内容

状态:免费试用

状态:免费试用 状态:免费试用

状态:免费试用University of Colorado Boulder

状态:预览

状态:预览Universitat Autònoma de Barcelona

状态:免费试用

状态:免费试用University of Colorado Boulder

人们为什么选择 Coursera 来帮助自己实现职业发展

Felipe M.

自 2018开始学习的学生

''能够按照自己的速度和节奏学习课程是一次很棒的经历。只要符合自己的时间表和心情,我就可以学习。'

Jennifer J.

自 2020开始学习的学生

''我直接将从课程中学到的概念和技能应用到一个令人兴奋的新工作项目中。'

Larry W.

自 2021开始学习的学生

''如果我的大学不提供我需要的主题课程,Coursera 便是最好的去处之一。'

Chaitanya A.

''学习不仅仅是在工作中做的更好:它远不止于此。Coursera 让我无限制地学习。'